d触发器电路?

一、d触发器电路?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

二、D触发器是什么稳态电路?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

三、利用D触发器设计延时电路?

一个触发器只能打一拍。

可以多级串联。

前一级的输出q接下一级的输入d。

CLK连在一起。

四、用门电路怎么构成D触发器?

用电平触发的SR触发器的S端与R端用一个非门连接就构成了D触发器。

五、电路为什么要有触发器这种结构?

为什么要有触发器这种结构?因为有需求!

在大规模的集成电路中,不但需要对二值逻辑进行算术运算和逻辑运算,还经常需要将这些信号和运算结果保存起来。为此,需要使用具有记忆功能的基本逻辑单元。能够存储一位二值逻辑信号的基本单元电路统称为触发器。

个人认为,我们可以把一块芯片,比如CPU,来比作人的大脑,可以进行计算,可以收发指令,而具有记忆,也是其功能的重要的一部分。

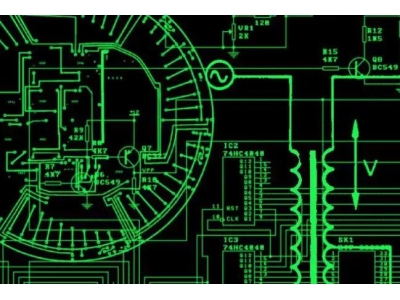

一个SR锁存器结构示意图如下:

由一个SR锁存器,再加上两个与非门(G3,G4)组成的输入控制电路,再加上控制时钟便组成了一个SR触发器。

在此说明一下计算机采用基于二进制的二值逻辑的原因:

① 数字符号表示简单容易,只要选用双态元件,如单向导电元件,磁性元件,发光元件,就可以十分简单地表示出数位上的数字0和1了;因此代价低廉,容易实现和使用。

② 运算规则简单,使计算机实现运算的逻辑结构构造简单。

③ 有利于逻辑运算的实现,可以用1表示真值,0表示假值,其运算是双值运算,与二进制完全一致。

为了实现记忆1位二值信号的功能,触发器必须具备以下两个特点:

1、具有两个能自行保持的稳定状态(也就是双稳态),用来表示逻辑状态的0和1,或二进制数的0和1。

2、在触发信号的操作下,根据不同的输入信号,可以置成0或1的状态。

实际电路中的应用:

逻辑电路可分为“组合”与“时序”两大类。“组合逻辑电路”,可高度概括为:无反馈、无记忆。自然,与其对应的“时序逻辑电路”便是:有反馈、有记忆。

如下图,在实际的电路设计中,是组合逻辑和时序逻辑共同完成的,组合逻辑计算出来的值由时序逻辑保存下来,经过同步时钟(CLK)来控制逻辑值的传递。

而触发器又可以根据功能,结构等分为不同的种类:

为什么要用时钟同步起来呢?

其实你想用异步电路也不是不可以,在此之前要理解同步电路和异步电路的区别:

同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

异步电路有很多优点,比如结构简单,面积小,速度快,功耗低,但是因为其易产生毛刺,大大降低了电路的可靠性,这在设计中是致命的!而同步设计是避免毛刺的最好方法!

另外,异步虽然不需要时钟,但是需要握手信号,在当今大规模集成电路的背景下,握手信号的复杂程度是难以想象的。

所以,同步电路依然是当前的主流设计!

作为一个理工科的学生,多学习,多思考是一个值得保持的好习惯,对于电路设计,不仅要理解它的功能,更要知道这样设计的初衷是什么,这样更有助于理解事物的本质,而非表象。

最后推荐几本数字电路相关书籍,堪称领域内的圣经,希望能对数字电路更进一步的理解有所帮助。

六、d锁存器和d触发器电路的动作特点?

D 型触发器的输入输出关系简单明了,是多位寄存器的基本结构。触发器是时钟上升沿(↑)触发,瞬间保存数据;锁存器是时钟高电平期间输出跟随输入变化,下降沿(↓)保存数据。 二者就是触发方式不同,适用于不同的场合。如 CPU 复用总线的地址锁存就是用锁存器。

七、用d触发器设计三人抢答电路

结构上,是主从触发器,由两个带使能端 D 触发器构成; · 性能上,是上升沿触发的边沿触发器,由上升沿前的 D 输入和当 时的状态决定...

八、图中的D触发器电路是什么意思?

因为D触发器受控于CP脉冲,也就是说受控于时钟脉冲,或者CP的上升沿或者CP的下降沿触发,所以称为时序电路

九、金卤灯的触发器电路图

金卤灯的触发器电路图

金卤灯是一种非常常见的照明设备,广泛应用于街道、广场、体育场等场所。这些灯具需要一个触发器电路来控制其正常工作,下面将介绍金卤灯的触发器电路图。

触发器电路简介

触发器电路是用来控制金卤灯启动和关闭的重要组成部分。金卤灯的光源是由一个气体放电管构成的,需要通过触发器电路来提供一个高压脉冲来启动放电。下面是金卤灯触发器电路的主要组成部分:

- 高压脉冲发生器:用来产生起始脉冲信号,激活金卤灯。

- 放电电容:对高压脉冲进行储存和释放。

- 触发线圈:触发金卤灯放电的关键部件。

金卤灯触发器电路的原理

金卤灯触发器电路的原理是利用高压脉冲发生器产生的高压脉冲信号,通过触发线圈的作用,使金卤灯放电电容带电,从而实现金卤灯的启动。

金卤灯触发器电路的工作原理如下:

- 当金卤灯需要启动时,高压脉冲发生器会产生高压脉冲信号。

- 高压脉冲信号经过放电电容的储存,电容带电。

- 带电的放电电容通过触发线圈,产生强磁场。

- 强磁场的作用下,金卤灯气体放电管中的气体被激发并放电,产生强烈光亮。

金卤灯触发器电路的原理比较简单,但其中涉及到的电路设计和参数选择需要根据具体情况进行灵活调整,确保触发器电路能够可靠启动金卤灯。

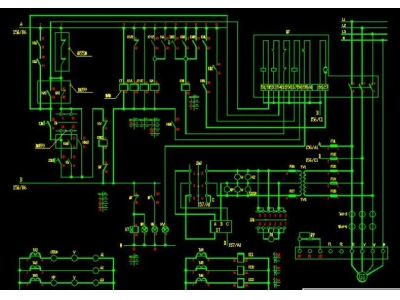

金卤灯触发器电路图示例

下面是一个金卤灯触发器电路的示例图:

在这个示例电路图中,R1、R2和C1构成了高压脉冲发生器,D1和C2构成了放电电容电路,L1为触发线圈。高压脉冲发生器产生的脉冲信号经过放电电容的储存,通过触发线圈产生磁场,触发金卤灯的放电。

金卤灯触发器电路的设计注意事项

设计金卤灯触发器电路时需要注意以下几点:

- 合理选择高压脉冲发生器的参数,确保能够提供足够的高压脉冲信号。

- 放电电容的容值和电压等级要与金卤灯的要求匹配。

- 触发线圈的设计需要考虑磁场的强度和金卤灯的起爆电流。

- 电路布局要合理,避免干扰和损耗。

总之,金卤灯触发器电路是金卤灯正常工作的关键部分,合理设计和选择电路参数可以确保金卤灯的可靠启动。希望通过本文的介绍,读者对金卤灯触发器电路有了更深入的了解。

参考资料:

- 金卤灯的触发器电路设计与参数选择,xxx杂志,2010年。

- 触发器电路的原理及应用,xxx出版社,2008年。

十、d触发器的电路符号图和真值表?

CP D Q^(n+1) ↑ 0 0 ↑ 1 1 在CP脉冲的上升沿(或者下降沿)的作用下,把D端的数据打入D触发器,