cmos门电路输入端接大电阻?

一、cmos门电路输入端接大电阻?

如果接到地就是相当于接低电平,因为CMOS的输入阻抗非常高(大致10^12欧姆) 1、CMOS输入端是不允许悬空的,必须要接到某个固定的电平上,否则极高的输入阻抗,会使输入端由于空间电磁场的影响产生高频振荡,甚至导致该器件的其它部分也不能正常工作。 2、接一个较大的电阻到地(或上拉),可以减低功耗(其它输出对这个端口的功耗),同时满足应用的要求。

觉得有用点个赞吧

二、cmos门电路的输入电阻?

在高阻态时,cmos门电路的输入电阻是无限大的。

三、门电路符号在word中如何输入?

门电路符号在word中是不太好直接输入的,如果一定要这样输入,你只有做出图形插入。

Office上做电路等,你应该使用Office Visio 这个软件,它是Office 家族成员之一,是专门制作电路图、流程图等等的专用软件,它做的图可直接转到WORD中去。

Microsoft 公式3.0 主要就是做公式,并没有做电路图的能力。

四、cmos门电路输入端接地会怎样?

CMOS逻辑门输入阻抗高,因此对干扰信号的扑捉能力也强。如果输入端悬空则很容易引入干扰。同时,由于输入管是MOS管的绝缘栅级,他与其他电极间的绝缘层很容易被击穿,外来的干扰信号可能会损坏元件。因此CMOS逻辑门的多余输入端绝不允许悬空。

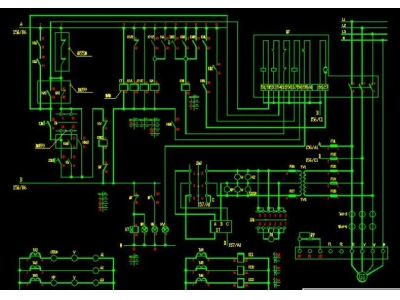

五、cmos门电路多余输入端处理方法?

对于CMOS与门、与非门电路的多余输入端就应采用高电平,即可通过限流电阻(500Ω)接电源

或门和或非门电路多余输入端的处理方法应是将多余输入端接低电平,即通过限流电阻(500Ω)接地

由于MOS管在电路中是一压控元件,基于这一特点,输入端信号易受外界干扰,所以在使用CMOS门电路时输入端特别注意不能悬空

六、与门电路输入0和1会输出什么?

与门电路输入0和1输出一定是零,与门只要有零输出一定是零

七、cmos门电路接地输入端是高电平吗?

CMOS门电路的接地输入端通常是高阻抗状态,而不是高电平。在CMOS电路中,接地输入端通常连接到电源的负极,以提供一个低阻抗的接地路径。这有助于防止由于静电放电或其他原因引起的噪声和干扰。因此,当您看到CMOS门电路中的接地输入端时,它通常不会显示为高电平,而是显示为低阻抗或接近于零的电阻值。

八、为什么CMOS集成门电路多余输入端不能悬空?

CMOS集成电路的输入阻抗相当高,输入端悬空,会受到感应信号干扰而误认为是有效输入信号,易出现错误的输出。

对于非CMOS电路,由于输入阻抗相对较低,而感应到的干扰信号相当于高阻抗输出,接入低阻抗输入端后信号基本衰减掉了。

为避免干扰产生的影响,通常采取将逻辑电路的空输入端接高电平或低电平的办法。

九、为什么ttl门电路的输入端经过电阻?

ttl逻辑门输入端通过小电阻入地,相当于接低电平;

通过大电阻入地,相当于接高电平;

如果接在vcc上,无论是直接相连、通过小电阻、通过大电阻,都是输入的高电平;

大电阻指的是大于“开门电阻”,小电阻指的是小于“关门电阻”。

oc门的输出相“线与”,两个oc门的输出只要有一个为0,则输出就是0,否则为1.

十、TTL门电路输入端通过电阻接地相当于输入什么电平?

TTL输入端是内部三极管发射极,其内部有基极上拉电阻,因此TTL输入端接低电平时有电流通过·输入端入地,这样才能输入低电平逻辑;如果输入端接大电阻或开路,输入端就会产生较大的电压降,当这个电压降接近或高于3.6V,TTL就会认为是输入高电平。