电路为什么要有触发器这种结构?

一、电路为什么要有触发器这种结构?

为什么要有触发器这种结构?因为有需求!

在大规模的集成电路中,不但需要对二值逻辑进行算术运算和逻辑运算,还经常需要将这些信号和运算结果保存起来。为此,需要使用具有记忆功能的基本逻辑单元。能够存储一位二值逻辑信号的基本单元电路统称为触发器。

个人认为,我们可以把一块芯片,比如CPU,来比作人的大脑,可以进行计算,可以收发指令,而具有记忆,也是其功能的重要的一部分。

一个SR锁存器结构示意图如下:

由一个SR锁存器,再加上两个与非门(G3,G4)组成的输入控制电路,再加上控制时钟便组成了一个SR触发器。

在此说明一下计算机采用基于二进制的二值逻辑的原因:

① 数字符号表示简单容易,只要选用双态元件,如单向导电元件,磁性元件,发光元件,就可以十分简单地表示出数位上的数字0和1了;因此代价低廉,容易实现和使用。

② 运算规则简单,使计算机实现运算的逻辑结构构造简单。

③ 有利于逻辑运算的实现,可以用1表示真值,0表示假值,其运算是双值运算,与二进制完全一致。

为了实现记忆1位二值信号的功能,触发器必须具备以下两个特点:

1、具有两个能自行保持的稳定状态(也就是双稳态),用来表示逻辑状态的0和1,或二进制数的0和1。

2、在触发信号的操作下,根据不同的输入信号,可以置成0或1的状态。

实际电路中的应用:

逻辑电路可分为“组合”与“时序”两大类。“组合逻辑电路”,可高度概括为:无反馈、无记忆。自然,与其对应的“时序逻辑电路”便是:有反馈、有记忆。

如下图,在实际的电路设计中,是组合逻辑和时序逻辑共同完成的,组合逻辑计算出来的值由时序逻辑保存下来,经过同步时钟(CLK)来控制逻辑值的传递。

而触发器又可以根据功能,结构等分为不同的种类:

为什么要用时钟同步起来呢?

其实你想用异步电路也不是不可以,在此之前要理解同步电路和异步电路的区别:

同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

异步电路有很多优点,比如结构简单,面积小,速度快,功耗低,但是因为其易产生毛刺,大大降低了电路的可靠性,这在设计中是致命的!而同步设计是避免毛刺的最好方法!

另外,异步虽然不需要时钟,但是需要握手信号,在当今大规模集成电路的背景下,握手信号的复杂程度是难以想象的。

所以,同步电路依然是当前的主流设计!

作为一个理工科的学生,多学习,多思考是一个值得保持的好习惯,对于电路设计,不仅要理解它的功能,更要知道这样设计的初衷是什么,这样更有助于理解事物的本质,而非表象。

最后推荐几本数字电路相关书籍,堪称领域内的圣经,希望能对数字电路更进一步的理解有所帮助。

二、d触发器电路?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

三、金卤灯的触发器电路图

金卤灯的触发器电路图

金卤灯是一种非常常见的照明设备,广泛应用于街道、广场、体育场等场所。这些灯具需要一个触发器电路来控制其正常工作,下面将介绍金卤灯的触发器电路图。

触发器电路简介

触发器电路是用来控制金卤灯启动和关闭的重要组成部分。金卤灯的光源是由一个气体放电管构成的,需要通过触发器电路来提供一个高压脉冲来启动放电。下面是金卤灯触发器电路的主要组成部分:

- 高压脉冲发生器:用来产生起始脉冲信号,激活金卤灯。

- 放电电容:对高压脉冲进行储存和释放。

- 触发线圈:触发金卤灯放电的关键部件。

金卤灯触发器电路的原理

金卤灯触发器电路的原理是利用高压脉冲发生器产生的高压脉冲信号,通过触发线圈的作用,使金卤灯放电电容带电,从而实现金卤灯的启动。

金卤灯触发器电路的工作原理如下:

- 当金卤灯需要启动时,高压脉冲发生器会产生高压脉冲信号。

- 高压脉冲信号经过放电电容的储存,电容带电。

- 带电的放电电容通过触发线圈,产生强磁场。

- 强磁场的作用下,金卤灯气体放电管中的气体被激发并放电,产生强烈光亮。

金卤灯触发器电路的原理比较简单,但其中涉及到的电路设计和参数选择需要根据具体情况进行灵活调整,确保触发器电路能够可靠启动金卤灯。

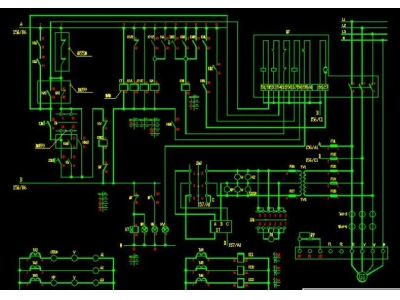

金卤灯触发器电路图示例

下面是一个金卤灯触发器电路的示例图:

在这个示例电路图中,R1、R2和C1构成了高压脉冲发生器,D1和C2构成了放电电容电路,L1为触发线圈。高压脉冲发生器产生的脉冲信号经过放电电容的储存,通过触发线圈产生磁场,触发金卤灯的放电。

金卤灯触发器电路的设计注意事项

设计金卤灯触发器电路时需要注意以下几点:

- 合理选择高压脉冲发生器的参数,确保能够提供足够的高压脉冲信号。

- 放电电容的容值和电压等级要与金卤灯的要求匹配。

- 触发线圈的设计需要考虑磁场的强度和金卤灯的起爆电流。

- 电路布局要合理,避免干扰和损耗。

总之,金卤灯触发器电路是金卤灯正常工作的关键部分,合理设计和选择电路参数可以确保金卤灯的可靠启动。希望通过本文的介绍,读者对金卤灯触发器电路有了更深入的了解。

参考资料:

- 金卤灯的触发器电路设计与参数选择,xxx杂志,2010年。

- 触发器电路的原理及应用,xxx出版社,2008年。

四、rs触发器电路结构?

rs触发器是构成其它各种功能触发器的基本组成部分。

rs触发器电路结构是把两个与非门或者或非门G₁、G₂的输入、输出端交叉连接。

rs触发器具有两个稳定状态,分别为1和0,称双稳态触发器。

如果没有外加触发信号作用,它将保持原有状态不变,触发器具有记忆作用。

在外加触发信号作用下,触发器输出状态才可能发生变化,输出状态直接受输入信号的控制。

五、单稳态触发器电路的电路参数?

单稳态触发器电路是一种有稳态和暂态的基本脉冲单元电路,没有外加触发信号时,电路处于稳态,外加触发信号时,电路从稳态翻转到暂态,经过一段时间后返回稳态。暂态时间取于电路中的参数包括电阻和电容的大小。

六、单极施密特触发器电路?

对于标准施密特触发器,当输入电压高于正向阈值电压,输出为高;当输入电压低于负向阈值电压,输出为低;当输入在正负向阈值电压之间,输出不改变,也就是说输出由高电准位翻转为低电准位,或是由低电准位翻转为高电准位对应的阈值电压是不同的。只有当输入电压发生足够的变化时,输出才会变化,因此将这种元件命名为触发器。这种双阈值动作被称为 迟滞现象,表明施密特触发器有记忆性。从本质上来说,施密特触发器是一种双稳态多谐振荡器。

施密特触发器可作为波形整形电路,能将模拟信号波形整形为数字电路能够处理的方波波形,而且由于施密特触发器具有滞回特性,所以可用于抗干扰,其应用包括在开回路配置中用于抗扰,以及在闭回路正回授/负回授配置中用于实现多谐振荡器。

七、rc单稳态触发器电路?

单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。

八、jk触发器实验电路连接方法?

JK触发器是一种常用的数字电路元件,用于存储和控制数字信号。以下是JK触发器实验电路连接方法的步骤:

1. 准备实验所需材料:JK触发器芯片、电阻、电容、开关、LED灯、面包板、电源等。

2. 将JK触发器芯片插入面包板上,注意芯片的方向和引脚位置。

3. 使用电阻和电容构建时钟信号电路,并将其与JK触发器的时钟输入端连接。

4. 使用开关构建输入端口电路,将其与JK触发器的J和K输入端连接。

5. 使用LED灯构建输出端口电路,将其与JK触发器的Q和Q'输出端连接。

6. 连接电源线,并将电源接口插入面包板上的电源接口孔中。

7. 打开电源开关,开始实验。

需要注意的是,在连接电路时需要仔细检查每个连接是否正确,以防止电路短路或者焊接错误导致损坏电路元件。同时,实验时需要按照实验步骤进行,不要随意更改电路连接方式,以免影响实验结果。

九、由触发器产生的电路是

触发器的电路图由逻辑门组合而成,其结构均由R-S锁存器派生而来(广义的触发器包括锁存器)。触发器可以处理输入、输出信号和时钟频率之间的相互影响。

在R-S锁存器的前面加一个由两个与门和一个非门构成的附加电路,则构成D触发器。当时钟脉冲CP为1时,读入输入端D的数据并传至输出端;当CP为0时,根据与门“只要有一个输入端为0则输出为0”的特性,输入端D的数据被与门屏蔽了,无法到达输出端,不管输入D怎样变化,Q端输出值都保持不变,只有等到下一个CP高电平到来时,才会把当前的D值送出。这样就实现了延迟输出即暂时保存的功能。从电路的动作可以看出,时钟输入端起到控制的作用,CP为1时,能触发后面的锁存器把D的值暂时锁存起来,这也正是触发器名词中“触发”的含义,这正是触发器与锁存器的联系与区别:触发器利用了锁存器的保存原理,但是加上了触发功能,可以控制保存的时间。

十、D触发器是什么稳态电路?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。